## Innogration (Suzhou) Co., Ltd.

## 3.0-5.0GHz, 10W, 28V High Gain GaN Fully matched PA Module

#### **Description**

The G2MAH3050-10C9 is a 10-watt **,2 stage/high gain** integrated Power Amplifier Module, designed for broad band applications, with frequencies from 3 to 5GHz. The module is 50  $\Omega$  input/output matched and requires minimal external components. It can work at higher voltage like 32V with increased power capability

The module implements wideband power amplifier in form of multi chips, housed in cost effective plastic open cavity package, offers a much lower cost than traditional MMIC solutions.

#### **Product Features**

• Operating Frequency Range: 3-5GHz

• Operating Drain Voltage: +28 V

• 50  $\Omega$  Input/Output

• Psat≥40 dBm

• Small signal gain:>25dB, Power gain:>22dB

• Minimum efficiency:>40%

• 12x10 mm Surface Mount Package

• Compliant to Restriction of Hazardous Substances (RoHS) Directive 2002/95/EC

#### **Applications**

- Ultra Broadband Amplifiers

- Fiber Drivers

- Test Instrumentation

- EMC Amplifier Drivers

- 2-way Radios

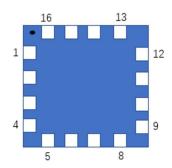

## Pin Configuration and Description (Top view)

| Pin No.      | Symbol | Description                                                                              |

|--------------|--------|------------------------------------------------------------------------------------------|

| 1            | RF IN  | RF Input                                                                                 |

| 9            | RF OUT | RF Output                                                                                |

| 16           | Vgs1   | Gate bias for 1 <sup>st</sup> stage                                                      |

| 15           | Vdd1   | Drain bias for 1 <sup>st</sup> stage                                                     |

| 6            | Vgs2   | Gate bias for 2nd stage                                                                  |

| 7            | Vdd2   | Drain bias for 2nd stage                                                                 |

| Others       | NC     | No connection                                                                            |

|              |        | DC/RF Ground. Proposed to be soldered to heatsink plane directly for the best CW thermal |

| Package Base | GND    | and RF performance. Soldered through high density vias or copper coin also allowed ,but  |

|              |        | will result in excessive junction temperatures and different RF performance              |

#### **Table 1. Maximum Ratings**

| Symbol                       | Value                                                    | Unit                                                                                                    |

|------------------------------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| $V_{\scriptscriptstyle DSS}$ | 150                                                      | Vdc                                                                                                     |

| $V_{\sf GS}$                 | -10 to +2                                                | Vdc                                                                                                     |

| $V_{DD}$                     | +36                                                      | Vdc                                                                                                     |

| Tstg                         | -65 to +150                                              | °C                                                                                                      |

| Tc                           | +150                                                     | °C                                                                                                      |

| T,                           | +225                                                     | °C                                                                                                      |

|                              | V <sub>DSS</sub> V <sub>GS</sub> V <sub>DD</sub> Tstg Tc | V <sub>DSS</sub> 150 V <sub>SS</sub> -10 to +2 V <sub>DD</sub> +36 Tstg -65 to +150 T <sub>C</sub> +150 |

#### **Table 2. Thermal Characteristics**

| Characteristic                                        | Symbol | Value | Unit |

|-------------------------------------------------------|--------|-------|------|

| Thermal Resistance, Junction to Case                  | Rejc   | 6     | 0000 |

| T <sub>C</sub> = 85°C, T <sub>J</sub> =175°C, DC test | RejC   | 6     | °C/W |

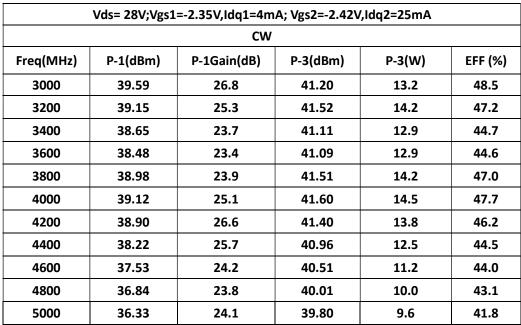

#### **Table 3. Electrical Characteristics**

| Parameter                                                                       | Condition | Min  | Тур | Max  | Unit |

|---------------------------------------------------------------------------------|-----------|------|-----|------|------|

| Frequency Range                                                                 |           | 3000 |     | 5000 | MHz  |

| Power Gain @ Psat                                                               |           | 23   |     |      | dB   |

| P <sub>SAT</sub>                                                                | Pulse     |      | 40  |      | dBm  |

| Drain Efficiency @ P <sub>SAT</sub>                                             |           | 40   |     |      | %    |

| Unless otherwise noted: TA = 25°C, Vpp =28 V, Pulse Width=50 us. Duty cycle=20% |           |      |     |      |      |

Load Mismatch of per Section (On Test Fixture, 50 ohm system): V<sub>DD</sub> =28 V, I<sub>DQ</sub> =25 mA, f = 3.5 GHz

| VSWR 10:1 at Psat pulse CW Output Power | No Device Degradation |

|-----------------------------------------|-----------------------|

|-----------------------------------------|-----------------------|

# Innogration (Suzhou) Co., Ltd.

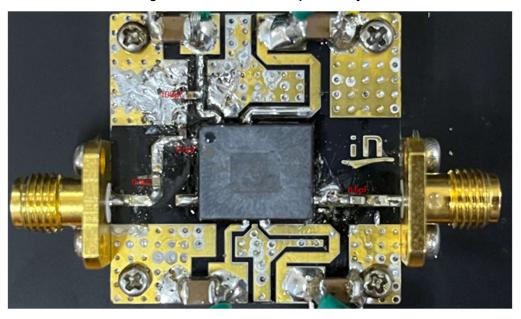

#### **Reference Circuit of Test Fixture Assembly Diagram**

Figure 1. Test Circuit Component Layout

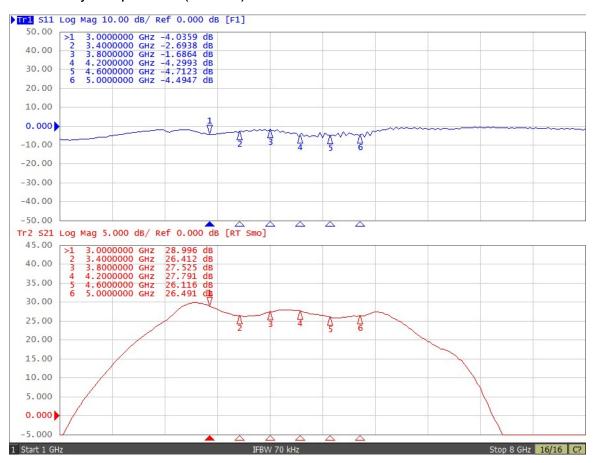

#### TYPICAL CHARACTERISTICS

Figure 2. Network analyzer output S11/S21 (Pin=0dBm)

# Innogration (Suzhou) Co., Ltd.

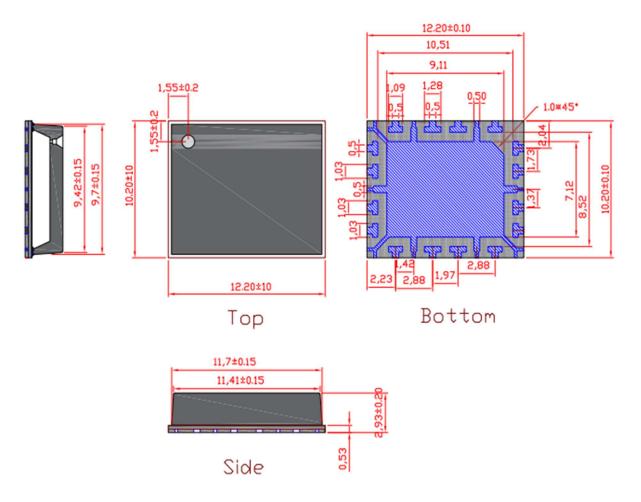

## Package Dimensions (Unit:mm)

#### **Revision history**

Table 6. Document revision history

| Date      | Revision | Datasheet Status         |

|-----------|----------|--------------------------|

| 2023/2/14 | Rev 1.0  | Preliminary Datasheet    |

| 2023/7/2  | Rev 1.1  | Modify the gain flatness |

|           |          |                          |

Application data based on HJ-23-02

#### **Disclaimers**

Specifications are subject to change without notice. Innogration believes the information contained within this data sheet to be accurate and reliable. However, no responsibility is assumed by Innogration for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Innogration . Innogration makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose. "Typical" parameters are the average values expected by Innogration in large quantities and are provided for information purposes only. These values can and do vary in different applications and actual performance can vary over time. All operating parameters should be validated by customer's technical experts for each application. Innogration products are not designed, intended or authorized for use as components in applications intended for surgical implant into the body or to support or sustain life, in applications in which the failure of the Innogration product could result in personal injury or death or in applications for planning, construction, maintenance or direct operation of a nuclear facility. For any concerns or questions related to terms or conditions, pls check with Innogration and authorized distributors Copyright © by Innogration (Suzhou) Co.,Ltd.